# **SUJET A**

#### Question 1

Dans un système 8 bits, quel est le complément à deux de la valeur décimale (-5)?

**A.** 10000101;

**B.** 11111010;

**C.** 11111011;

**D.** 10001011

#### Question 2

Une architecture Harvard se caractérise par :

- A. Une mémoire unifiée pour les instructions et les données

- B. Des mémoires séparées pour les instructions et les données

- C. Un bus de données et un bus d'adresses limités à 32 bits ;

D. L'absence d'étages de pipeline

# Question 3

Qu'est-ce qui détermine si une instruction conditionnelle est exécutée dans un Cortex-M3?

A. L'état de la pile ;

**B.** Le compteur d'instructions ;

C. La structure de la mémoire

D. Les drapeaux du registre d'état du programme

#### Question 4

Une instruction conditionnelle s'écrit en ajoutant au code de l'instruction :

A. Un préfixe "IF";

B. Un paramètre d'adresse mémoire

C. Un mot-clé LOOP; D. Un suffixe conditionnel comme EQ, NE, GT, etc.

# Question 5

Dans le Cortex-M3, une branche conditionnelle BEQ est exécutée lorsque :

A. Le drapeau N (Negative) est à 1 ; B. Le drapeau C (Carry) est à 1

C. Le drapeau Z (Zero) est à 1 ;

D. Le drapeau V (Overflow) est à 1

#### Question 6

Combien d'instructions peuvent être conditionnellement exécutées après un IT?

**A.** 1;

**B.** 2; C. 5; D. Jusqu'à 4;

### Question 7

Dans un système 8 bits, quel est le plus grand entier signé positif en complément à deux ?

A. 255; B. 128; C. 127; D. 64

## **Question 8**

Pour obtenir le complément à deux d'un nombre binaire positif, il faut :

A. inverser tous les bits ; B. inverser tous les bits et ajouter 1

C. inverser uniquement le bit de poids fort ; D. Soustraire 1 puis inverser tous les bits

#### Question 9

Le mode d'adressage "post-incrémentation" dans une instruction de transfert mémoire permet :

A. D'incrémenter le registre d'adresse après l'opération ;

B. D'incrémenter le registre d'adresse avant l'opération

C. D'accéder uniquement à des adresses impaires ; D. D'accélérer l'exécution de l'opération

#### Question 10

Une instruction conditionnelle ADDNE dans un Cortex-M3 est exécutée si :

A. Le dernier résultat est différent de zéro ; B. Le drapeau N est inactif (N=0)

C. Le drapeau C est actif (C=1); D. Le dernier résultat est égal à zéro

#### Question 11

Dans le Cortex-M3, l'instruction BL est utilisée pour :

A. Réaliser un branchement conditionnel; B. Répéter un bloc d'instructions

C. Appeler une fonction et sauvegarder l'adresse de retour ;

D. Modifier directement un drapeau du registre d'état

#### Question 12

Lors de l'exécution d'un sous-programme, l'adresse de retour est sauvegardée dans :

A. La pile; B. Le registre PC; C. Une zone mémoire bien spécifique; D. Le registre LR

# **Question 13**

Supposons que les registres du Cortex-M3 contiennent les valeurs suivantes :

R0 = 0x00000005; R1 = 0x0000000A; R2=0x00000002

Instruction à exécuter : ADDEQ R2, R0, R1

Quelle est la valeur de R2 si le drapeau Z (Zero) dans le registre d'état est à « 1 » :

**A.** R2=0x00000002;

**B.** R2=0x0000000F; **C.** R2=0xFFFFFFF;

**D.** R2=0x00000015

### Question 14

Supposons que les registres du Cortex-M3 contiennent les valeurs suivantes :

R0 = 0xFF00FF00; R1 = 0x00FF00FF; R2=0x12345678

Instruction à exécuter : ORREQ R2, R0, R1

Quelle est la valeur de R2 si le drapeau Z (Zero) dans le registre d'état est à « 1 » :

**A.** R2=0x12345678; **B.** R2=0x FF00FF00; **C.** R2=0xFFFFFFFF; **D.** R2=0x00FF00FF

#### **Question 15**

Supposons que les registres du Cortex-M3 contiennent les valeurs suivantes :

R0 = 0x00000010; R1 = 0x000000020; R2 = 0x000000030; R3 = 0x00000040

Liste d'instructions exécutées :

CMP RO, R1

**BGT** suite

ADD R2, R0, R1

SUB R3, R1, R0

Les nouvelles valeurs de R2 et R3 après exécution de ce programme sont :

**A.** R2=0x00000030 et R3 =0x00000040;

**B.** R2=0x00000030 et R3 =0x00000010;

**C.** R2=0x00000030 et R3 =0x00000020; **D.** R2=0x00000030 et R3 =0x00000010

# SUJET B

#### Question 1

Combien d'instructions peuvent être conditionnellement exécutées après un IT ?

**A.** 1;

- B. 2;

- C. 5;

- D. Jusqu'à 4;

# Question 2

Dans un système 8 bits, quel est le plus grand entier signé positif en complément à deux ?

**A.** 255;

- **B.** 128;

- C. 127;

- D. 64

# Question 3

Pour obtenir le complément à deux d'un nombre binaire positif, il faut :

A. inverser tous les bits ;

B. inverser tous les bits et ajouter 1

C. inverser uniquement le bit de poids fort ; D. Soustraire 1 puis inverser tous les bits

### Question 4

Le mode d'adressage "post-incrémentation" dans une instruction de transfert mémoire permet :

- A. D'incrémenter le registre d'adresse après l'opération ;

- B. D'incrémenter le registre d'adresse avant l'opération

- C. D'accéder uniquement à des adresses impaires ;

- D. D'accélérer l'exécution de l'opération

#### Question 5

Une instruction conditionnelle ADDNE dans un Cortex-M3 est exécutée si :

A. Le dernier résultat est différent de zéro ; B. Le drapeau N est inactif (N=0)

C. Le drapeau C est actif (C=1);

D. Le dernier résultat est égal à zéro

#### Question 6

Dans le Cortex-M3, l'instruction BL est utilisée pour :

A. Réaliser un branchement conditionnel;

B. Répéter un bloc d'instructions

- C. Appeler une fonction et sauvegarder l'adresse de retour ;

- D. Modifier directement un drapeau du registre d'état

#### Question 7

Lors de l'exécution d'un sous-programme, l'adresse de retour est sauvegardée dans :

A. La pile; B. Le registre PC; C. Une zone mémoire bien spécifique; D. Le registre LR

# **Question 8**

Dans un système 8 bits, quel est le complément à deux de la valeur décimale -5 ?

**A.** 10000101; **B.** 11111010; **C.** 11111011; **D.** 10001011

### **Question 9**

Une architecture Harvard se caractérise par :

A. Une mémoire unifiée pour les instructions et les données

B. Des mémoires séparées pour les instructions et les données

C. Un bus de données et un bus d'adresses limités à 32 bits ; D. L'absence d'étages de pipeline

#### Question 10

Qu'est-ce qui détermine si une instruction conditionnelle est exécutée dans un Cortex-M3?

A. L'état de la pile ; B. Le compteur d'instructions ; C. La structure de la mémoire

D. Les drapeaux du registre d'état du programme

### Question 11

Une instruction conditionnelle s'écrit en ajoutant au code de l'instruction :

A. Un préfixe "IF"; B. Un paramètre d'adresse mémoire

C. Un mot-clé LOOP; D. Un suffixe conditionnel comme EQ, NE, GT, etc.

# Question 12

Dans le Cortex-M3, une branche conditionnelle BEQ est exécutée lorsque :

A. Le drapeau N (Negative) est à 1 ; B. Le drapeau C (Carry) est à 1

C. Le drapeau Z (Zero) est à 1; D. Le drapeau V (Overflow) est à 1

# Question 13

Supposons que les registres du Cortex-M3 contiennent les valeurs suivantes :

R0 = 0xFF00FF00; R1 = 0x00FF00FF; R2=0x12345678

Instruction à exécuter : ORREQ R2, R0, R1

Quelle est la valeur de R2 si le drapeau Z (Zero) dans le registre d'état est à « 1 » :

**A.** R2=0x12345678; **B.** R2=0x FF00FF00; **C.** R2=0xFFFFFFF; **D.** R2=0x00FF00FF

## Question 14

Supposons que les registres du Cortex-M3 contiennent les valeurs suivantes :

R0 = 0x00000005; R1 = 0x0000000A; R2=0x00000002

Instruction à exécuter : ADDEQ R2, R0, R1

Quelle est la valeur de R2 si le drapeau Z (Zero) dans le registre d'état est à « 1 » :

**A.** R2=0x00000002; **B.** R2=0x0000000F; **C.** R2=0xFFFFFFF; **D.** R2=0x00000015

# Question 15

Supposons que les registres du Cortex-M3 contiennent les valeurs suivantes :

R0 = 0x00000010; R1 = 0x000000020; R2 = 0x00000030; R3 = 0x00000040

Liste d'instructions exécutées :

CMP RO, R1

**BGT** suite

ADD R2, R0, R1

suite SUB R3, R1, R0

Les nouvelles valeurs de R2 et R3 après exécution de ce programme sont :

**A.** R2=0x00000030 et R3 =0x00000040; **B.** R2=0x00000030 et R3 =0x00000010;

**C.** R2=0x00000030 et R3 =0x00000020; **D.** R2=0x00000030 et R3 =0x00000010

# **SUJET C**

#### Question 1

Qu'est-ce qui détermine si une instruction conditionnelle est exécutée dans un Cortex-M3?

- A. L'état de la pile ;

- B. Le compteur d'instructions ; C. La structure de la mémoire

- D. Les drapeaux du registre d'état du programme

# Question 2

Une instruction conditionnelle s'écrit en ajoutant au code de l'instruction :

- A. Un préfixe "IF";

- B. Un paramètre d'adresse mémoire

- C. Un mot-clé LOOP ; D. Un suffixe conditionnel comme EQ, NE, GT, etc.

# Question 3

Dans le Cortex-M3, une branche conditionnelle BEQ est exécutée lorsque :

- A. Le drapeau N (Negative) est à 1 ; B. Le drapeau C (Carry) est à 1

- C. Le drapeau Z (Zero) est à 1 ; D. Le drapeau V (Overflow) est à 1

# Question 4

Supposons que les registres du Cortex-M3 contiennent les valeurs suivantes :

R0 = 0xFF00FF00; R1 = 0x00FF00FF; R2=0x12345678

Instruction à exécuter : ORREQ R2, R0, R1

Quelle est la valeur de R2 si le drapeau Z (Zero) dans le registre d'état est à « 1 » :

**A.** R2=0x12345678; **B.** R2=0x FF00FF00; **C.** R2=0xFFFFFFF; **D.** R2=0x00FF00FF

#### Question 5

Supposons que les registres du Cortex-M3 contiennent les valeurs suivantes :

R0 = 0x00000005; R1 = 0x0000000A; R2=0x00000002

Instruction à exécuter : ADDEQ R2, R0, R1

Quelle est la valeur de R2 si le drapeau Z (Zero) dans le registre d'état est à « 1 » :

**A.** R2=0x00000002; **B.** R2=0x0000000F; **C.** R2=0xFFFFFFF; **D.** R2=0x00000015

### Question 6

Supposons que les registres du Cortex-M3 contiennent les valeurs suivantes :

R0 = 0x00000010; R1 = 0x000000020; R2 = 0x000000030; R3 = 0x00000040

Liste d'instructions exécutées :

CMP RO, R1

**BGT** suite

ADD R2, R0, R1

suite

SUB R3, R1, R0

Les nouvelles valeurs de R2 et R3 après exécution de ce programme sont :

**A.** R2=0x00000030 et R3 =0x00000040;

**B.** R2=0x00000030 et R3 =0x00000010;

**C.** R2=0x00000030 et R3 =0x00000020; **D.** R2=0x00000030 et R3 =0x00000010

# Question 7

Combien d'instructions peuvent être conditionnellement exécutées après un IT?

A. 1;

B. 2;

C. 5;

D. Jusqu'à 4;

### **Question 8**

Dans un système 8 bits, quel est le plus grand entier signé positif en complément à deux ?

**A.** 255;

**B.** 128;

**C.** 127;

**D.** 64

# Question 9

Pour obtenir le complément à deux d'un nombre binaire positif, il faut :

A. inverser tous les bits ;

**B.** inverser tous les bits et ajouter 1

C. inverser uniquement le bit de poids fort ; D. Soustraire 1 puis inverser tous les bits

# Question 10

Une instruction conditionnelle ADDNE dans un Cortex-M3 est exécutée si :

A. Le dernier résultat est différent de zéro ; B. Le drapeau N est inactif (N=0)

C. Le drapeau C est actif (C=1);

D. Le dernier résultat est égal à zéro

### Question 11

Dans le Cortex-M3, l'instruction BL est utilisée pour :

A. Réaliser un branchement conditionnel;

B. Répéter un bloc d'instructions

- C. Appeler une fonction et sauvegarder l'adresse de retour ;

- D. Modifier directement un drapeau du registre d'état

### Question 12

Lors de l'exécution d'un sous-programme, l'adresse de retour est sauvegardée dans :

A. La pile; B. Le registre PC; C. Une zone mémoire bien spécifique; D. Le registre LR

## Question 13

Dans un système 8 bits, quel est le complément à deux de la valeur décimale -5 ?

A. 10000101; B. 11111010; C. 11111011; D. 10001011

# Question 14

Une architecture Harvard se caractérise par :

- A. Une mémoire unifiée pour les instructions et les données

- B. Des mémoires séparées pour les instructions et les données

- C. Un bus de données et un bus d'adresses limités à 32 bits ; D. L'absence d'étages de pipeline

#### **Question 15**

Le mode d'adressage "post-incrémentation" dans une instruction de transfert mémoire permet :

- A. D'incrémenter le registre d'adresse après l'opération ;

- **B.** D'incrémenter le registre d'adresse avant l'opération

- C. D'accéder uniquement à des adresses impaires ; D. D'accélérer l'exécution de l'opération

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

# Elec3A / Architecture

Examen (Durée : 1 heure) ; Cours, TDs. et TPs. autorisés au format papier uniquement.

# Exercice I (QCM):

Voir sujet ci-joint. Donnez vos réponses sur la feuille dédiée à ça et fournie avec le sujet d'examen. Il faut hachurer **proprement** toute la case correspondant à la bonne réponse (A, B, C ou D). A la fin de l'examen, remettre vos réponses ainsi que le sujet d'examen (partie QCM) dans la copie.

**Exercice II:** Programmation en assembleur pour ARM Cortex-M3

L'objectif est de coder un programme en assembleur ARM Cortex-M3 qui assurer les opérations suivantes :

- (1) Lire une valeur entière N depuis une adresse mémoire (0x20000000).

- (2) Si N≤0, alors écrire 0 à l'adresse mémoire 0x20000004 (résultat) et terminer.

- (3) Sinon, calculer la somme des nombres entiers de 1 à N (c'est-à-dire somme=1+2+...+N).

- (4) Écrire la somme ainsi calculée à l'adresse mémoire 0x20000004 (résultat) et terminer.

Voici l'organigramme correspondant :

- (1) Début

- (2) Charger N depuis 0x20000000

- (3) N≤0 ?

- Oui  $\rightarrow$  Écrire 0 dans 0x20000004, puis brancher vers *fin*

- Non → Aller à l'étape suivante

- (4) Initialiser la somme S=0

- (5) Ajouter (faire la somme) 1,2,...,N à S

- (6) Écrire S dans 0x20000004

- (7) fin

### Travail demandé:

Traduire cet organigramme en programme assembleur pour le Cortex-M3.

Utiliser des boucles et des comparaisons conditionnelles.

Tester (à la main) votre programme avec les valeurs suivantes pour  $N:-5,\,0,\,5.$  A chaque cas, donner le résultat mis à l'adresse 0x20000004

Ordinateurs, Portable et connexion à internet interdits. Cours, TD et TP autorisés

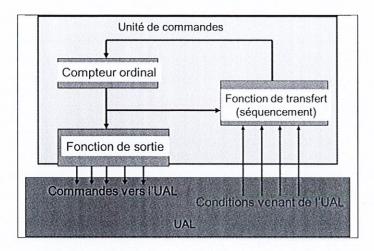

# Exo1: (2 points) On a le schéma fonctionnel d'un système complexe

- 1) A quoi sert le bloc commande?

- 2) A quoi sert le bloc UAL?

- 3) Expliquer le principe de fonctionnement du compteur Ordinal

- 4) Quel est la définition d'un bus, cité un exemple

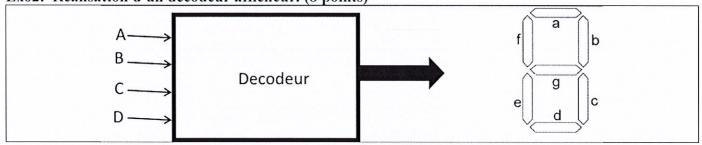

Exo2: Réalisation d'un décodeur afficheur. (8 points)

Figure 1 : Décodeur afficheur

On cherche à réaliser un décodeur DCB-afficheur à sept segments suivant le schéma de principe de la figure 1 ci-dessus. Les nombres de 0 à 15 codés en binaire sont entrés en D, C, B, A (D est le bit le plus significatif). Les sorties commandent l'allumage des segments d'un afficheur constitué de diodes a, b, .., g (figure 1) avec la règle suivante: mettre, en sortie du décodeur, la sortie à 1, entraîne l'allumage du segment a.

- 1) Donner les règles d'allumage permettant de représenter les chiffres de 0 à 15 en code hexadécimal :

- 0 ; 1 ; 2 ; 3 ; 4 ; 5 ; 6 ; 7 ; 8 ; 9 ; 10 ; 11 ; 12 ; 13 ; 14 ; 15

Exemple pour 10 : II on représente uniquement les LED allumées

2) Ecrire la table de vérité du décodeur dans l'ordre D, C, B, A, a, b, c, d, e, f, g.

|   | Variables entrée |   |   |  |   | Variables sorties |   |   |   |   |   |  |

|---|------------------|---|---|--|---|-------------------|---|---|---|---|---|--|

| D | С                | В | Α |  | a | b                 | С | d | e | f | g |  |

|   |                  |   | 3 |  |   |                   |   |   |   |   |   |  |

|   |                  |   |   |  |   |                   |   |   |   |   |   |  |

- 3) Déduire les 7 fonctions a, b, c, d, e, f, g. correspondantes.

- 4) Construire le logigramme de la fonction e en porte NAND.