# Examen final : Le langage VHDL Licence 3 SPI Elec - Session 1 - 20 Mai 2025 - Durée: 2 heures Conditions de l'examen

#### Permis:

• Documents imprimés ou manuscrits de cours, TD et TP de l'UBE.

### Interdit:

• Appareils électroniques avec accès à Internet (téléphone, tablette, montre connecté...)

#### **Exercice 1 : (6.5 pts)**

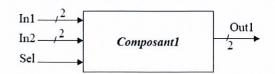

1. Donner en VHDL la description de *l'entité du Composant1* ci-contre.

2. Recopiez le code VHDL ci-dessous en corrigeant toutes les *erreurs de syntaxe* existantes.

3. Recopiez le code VHDL ci-dessous en corrigeant tous les *problèmes de synthèse* existants.

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

use IEEE.NUMERIC STD.ALL;

entity Circuit2 is

Port ( A : in STD LOGIC VECTOR (3 downto 0);

B : in STD LOGIC VECTOR (3 downto 0);

C : out STD_LOGIC_VECTOR (3 downto 0));

end Circuit2;

architecture Behavioral of Circuit2 is

signal i, j : integer:= 0;

signal ul, u2 : unsigned(2 downto 0);

begin

ul <= A ;

u2 <= B;

i <= u1 + u2 ;

C <= i ;

end Behavioral;

```

## Exercice 2: (5.5 pts)

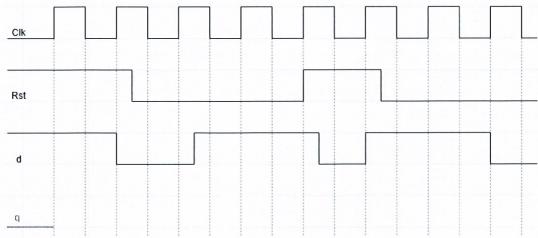

Pour simuler le comportement de la bascule D asynchrone décrite par le code VHDL du Circuit1 (question 1.2) on utilise un banc de test (testbench).

- 1. Donnez le process de simulation adapté pour générer les stimuli ci-dessous.

- 2. Recopiez les stimuli sur votre copie en complétant le signal de sortie q.

## vercice 3 : (8 nts)

a) C/C++ d) Verilog

| la ou les bonnes réponses.                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fichier utilisé pour la simulat                                                                                                                                                                                      | ion (test bench)?                                                                                                                                                                                                                                                                                                                                           |

| b) .xise                                                                                                                                                                                                             | c) .ise                                                                                                                                                                                                                                                                                                                                                     |

| e) .hdl                                                                                                                                                                                                              | f) .ieee                                                                                                                                                                                                                                                                                                                                                    |

| Question 2 : Lequel des composants suivants ne pourra pas être fabriqué avec des instructions uniquement concurrentes ?                                                                                              |                                                                                                                                                                                                                                                                                                                                                             |

| b) Un Décodeur                                                                                                                                                                                                       | c) Un Additionneur                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                      | f) Aucune de ces réponses                                                                                                                                                                                                                                                                                                                                   |

| Question 3: Quel est l'opérateur en VHDL qui permet de réaliser un décalage à droite ou à gauche, c'est-à-dire une multiplication ou une division par une puissance de 2.  a) << et >> b) srl et sll c) rolr et roll |                                                                                                                                                                                                                                                                                                                                                             |

| ,                                                                                                                                                                                                                    | f) shiftr et shiftl                                                                                                                                                                                                                                                                                                                                         |

| e) follingt et follingt                                                                                                                                                                                              | 1) Siliti et siliti                                                                                                                                                                                                                                                                                                                                         |

| Question 4 : En VHDL, le type : Integer est-il synthétisable, si on l'utilise dans un port ?  a) oui b) non                                                                                                          |                                                                                                                                                                                                                                                                                                                                                             |

| nar est-il synthétisable, si on l'<br>b) non                                                                                                                                                                         | utilise dans un port ?                                                                                                                                                                                                                                                                                                                                      |

| Question 6 : En VHDL deux process différents peuvent modifier le même signal en utilisant des conditions différentes                                                                                                 |                                                                                                                                                                                                                                                                                                                                                             |

| b) non                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                             |

| Question 7: En VHDL la bonne syntaxe pour une comparaison «inférieur ou égal» est :                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                             |

| b) if (a < < b)                                                                                                                                                                                                      | c) if (a<+=b)                                                                                                                                                                                                                                                                                                                                               |

| e) if (a <b a="b)&lt;/td" or=""><td>f) if (a inforequal b)</td></b>                                                                                                                                                  | f) if (a inforequal b)                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                      | e) .hdl s suivants ne pourra pas être fa b) Un Décodeur e) Un Multiplicateur n VHDL qui permet de réalis on ou une division par une pur b) srl et sll e) rollingr et rollingl steger est-il synthétisable, si on har est-il synthétisable, si on l' b) non ess différents peuvent modifie b) non entaxe pour une comparaison of b) if (a< <b)< td=""></b)<> |

Question 8 : Citer un autre langage permettant de programmer un FPGA (autre que VHDL).

c) WebGL

f) Python

b) JavaScript

e) Java